Examensarbete 20 p Oktober 2005

# A distributed ISA bus network using FPGAs and LVDS links

Johan Johansson

#### Teknisk- naturvetenskaplig fakultet UTH-enheten

Besöksadress: Ångströmlaboratoriet Lägerhyddsvägen 1 Hus 4, Plan 0

Postadress: Box 536 751 21 Uppsala

Telefon: 018 - 471 30 03

Telefax: 018 - 471 30 00

Hemsida: http://www.teknat.uu.se/student

#### Abstract

## A distributed ISA bus network using FPGAs and LVDS links

Johan Johansson

This master thesis describes the design of a distributed network with the purpose to evolve into a complete test system to test motherboards and similar units. The network encapsulates signals from an ISA bus and distributes it through a LVDS link. The LVDS network distributing the ISA bus protocol is supposed to run several meters and consist of several slave nodes testing the interfaces of the motherboards. The logic in this design is successfully implemented by the use of Field Programmable Gate Arrays (FPGAs). The advantage of using FPGAs is that they are easily configured and that they support LVDS on chip. LVDS is a differential signalling standard that support high throughput while it consumes low power.

The result of this work is a design that supports the protocols ISA, RS232 and I2C. The nodes in the network also consist of simple digital inputs and outputs. These are directly accessed through the ISA protocol.

The network design is built in a modular manner that makes it very easy to add more registers and protocols. This quality will play an important role when expanding the features of the network. If a protocol has to be added, a module supporting this standard is programmed. Then the module is added to the main logic via internal registers, all accessed via the ISA bus. The strong features in this distributed network design is the flexibility using modules, the support of high speed and the great configurability of the FPGAs.

Handledare: Erik Jansson, Hectronic AB Ämnesgranskare: Leif Gustafsson, UTH Examinator: Thomas Nyberg, UTH ISSN: 1401-5757, UPTEC F05 072 Tryckt av: Ångströmslaboratoriet, Uppsala Universitet

## Table of contents

| TABLE OF CONTENTS                                                                                                          | 1  |

|----------------------------------------------------------------------------------------------------------------------------|----|

| FIGURES                                                                                                                    | 5  |

| TABLES                                                                                                                     | 7  |

| CHAPTER 1 – INTRODUCTION                                                                                                   | 8  |

| <b>1.1 The present test system</b>                                                                                         |    |

| <ul> <li>1.2 Requirements for a new test system</li></ul>                                                                  |    |

| 1.3 The aim of this project                                                                                                |    |

| 1.4 Method description                                                                                                     |    |

| CHAPTER 2 – BACKGROUND                                                                                                     | 11 |

| 2.1 The OSI seven-layer model                                                                                              |    |

| <ul> <li>2.2 Backplane architecture</li></ul>                                                                              |    |

| 2.3 FPGA technology                                                                                                        |    |

| <ul> <li>2.3.1 FPGA introduction</li></ul>                                                                                 |    |

| 2.4 The ISA bus                                                                                                            |    |

| <ul><li>2.4.1 Introduction</li><li>2.4.2 ISA bus device communication</li><li>2.4.3 ISA bus interrupt signalling</li></ul> |    |

| <ul> <li>2.5 LVDS</li></ul>                                                                                                |    |

| 2.5.4 Data rates supported by LVDS in different applications                                                               |    |

| CHAPTER 3 – THE DISTRIBUTED ISA BUS NETWORK DESIGN                         | 30 |

|----------------------------------------------------------------------------|----|

| 3.1 Preliminary work – designing the distributed network                   | 30 |

| 3.1.1 Main system interface                                                |    |

| 3.1.2 Backplane architecture                                               |    |

| 3.1.3 The chosen logic in the test system                                  |    |

| 3.1.4 ISA backplane design                                                 |    |

| 3.1.5 Conclusion                                                           |    |

| 3.2 Introduction to the distributed ISA bus network design                 |    |

| 3.2.1 Communication flow                                                   |    |

| 3.2.2 The design described using the OSI model                             | 35 |

| 3.3 Internal system communication                                          |    |

| 3.3.1 Serial data block between nodes                                      |    |

| 3.3.2 Asynchronous communication between the modules and the state machine | 37 |

| 3.4 The modules                                                            |    |

| 3.4.1 The internal register managers                                       |    |

| 3.4.2 LVDS in and out modules                                              |    |

| 3.4.3 Cascaded DCMs                                                        |    |

| 3.4.4 RS232 controller                                                     |    |

| 3.4.5 I <sup>2</sup> C slave controller                                    |    |

| 3.4.6 Timers                                                               |    |

| 3.4.7 ISA slave                                                            |    |

| 3.4.8 ISA master                                                           | 44 |

| 3.5 The master node                                                        |    |

| 3.5.1 The communication flow in the master node                            |    |

| 3.5.2 Timing and area constraints                                          |    |

| 3.5.3 FPGA resource utilisation                                            | 48 |

| 3.6 The slave node                                                         |    |

| 3.6.1 The communication flow in the slave node                             |    |

| 3.6.2 Timing and area constraints                                          |    |

| 3.6.3 FPGA resource utilisation                                            |    |

| 3.7 Physical channel distribution and voltage levels                       |    |

| 3.7.1 Voltage levels                                                       |    |

| 3.7.2 LVDS link distribution                                               |    |

| 3.8 Timing analysis of the distributed network                             |    |

| 3.8.1 Access time for a device on the distributed ISA bus                  |    |

| 3.8.2 Access time for an internal register                                 | 55 |

| CHAPTER 4 – RESULTS                                                        | 56 |

| 4.1 Software related trouble shooting and solved problems                  | 56 |

| 4.1.1 Generation of high speed LVDS in a low cost FPGA                     |    |

| 4.1.2 Synchronising asynchronous signals before entering a state machine   |    |

| 4.1.3 Generation of high-speed clock signals                               | 56 |

| 4.2 Timing analysis of the design                                          | 56 |

| 4.3 Evaluation software                                                    | 59 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 60                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.4.1 ISA reset and IO16# signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                       |

| 4.4.2 LVDS bus termination problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60                                                                                                                                                                    |

| 4.4.3 Stabilising the LVDS channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                       |

| 4.4.4 FPGA breakdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                       |

| 4.5 Hardware evaluation of the design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                       |

| 4.5.1 Oscilloscope plots of ISA bus transmissions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                       |

| 4.5.2 Oscilloscope plots of LVDS bus transmissions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                       |

| 4.5.3 Test using two Spartan 3 starter kit boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                       |

| 4.5.4 Test using one Hectronic H4070 board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                       |

| 4.5.5 Test using two Hectronic H4070 boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                       |

| CHAPTER 5 – CONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 70                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                     |

| 5.1 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 70                                                                                                                                                                    |

| 5.2 The next step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70                                                                                                                                                                    |

| 5.2 The next step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 70                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                       |

| CHAPTER 6 – DISCUSSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72                                                                                                                                                                    |

| 6.1 The future test system design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 72                                                                                                                                                                    |

| 6.1.1 Two examples of test configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                       |

| 6.1.2 Implementation of a center node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                       |

| 6.1.3 A bigger FPGA instead of two smaller ones                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                       |

| 6.1.4 Steps needed to develop a complete test system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                       |

| 0.1.4 Steps needed to develop a complete test system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75                                                                                                                                                                    |

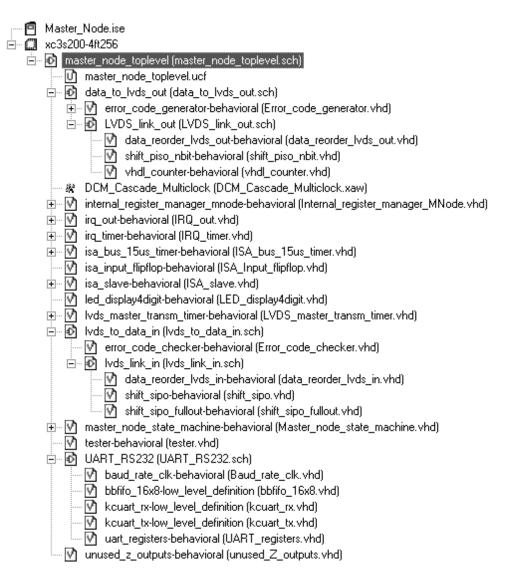

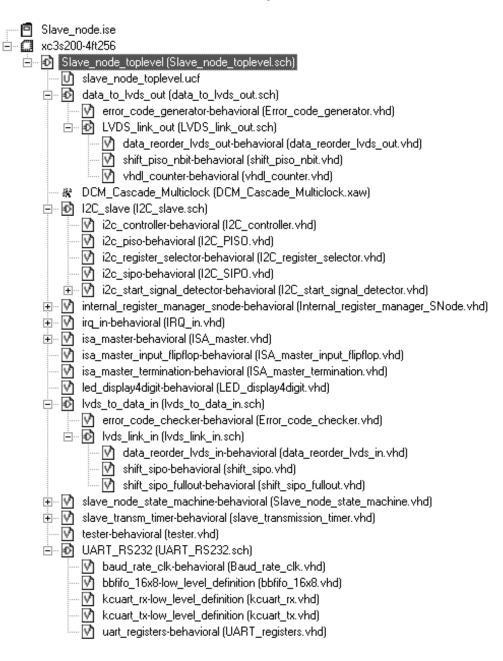

| APPENDIX A – DESIGN HIERARCHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 77                                                                                                                                                                    |

| APPENDIX A – DESIGN HIERARCH I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                       |

| A.1 Master hode code merarchy<br>A.2 Slave node code hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | / 0                                                                                                                                                                   |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                       |

| APPENDIX B – SOURCE CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79                                                                                                                                                                    |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>79</b><br>79                                                                                                                                                       |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <b>79</b><br>79<br>79                                                                                                                                                 |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>79</b><br>79<br>79<br>80                                                                                                                                           |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>79</b><br>79<br>79<br>80<br>81                                                                                                                                     |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>79</b><br>79<br>80<br>81<br>81                                                                                                                                     |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>79</b><br>79<br>80<br>81<br>81<br>83                                                                                                                               |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd<br>B.7 IRQ_timer.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                           | 79<br>79<br>80<br>81<br>81<br>83<br>86                                                                                                                                |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd<br>B.7 IRQ_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd                                                                                                                                                                                                                                                                                                                                                                                                             | <b>79</b><br><b>79</b><br><b>80</b><br><b>81</b><br><b>81</b><br><b>83</b><br><b>86</b><br><b>86</b>                                                                  |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd<br>B.7 IRQ_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.9 ISA_Input_flipflop.vhd                                                                                                                                                                                                                                                                                                                                                                               | <b>79</b><br><b>79</b><br><b>80</b><br><b>81</b><br><b>81</b><br><b>83</b><br><b>86</b><br><b>86</b>                                                                  |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd<br>B.7 IRQ_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.9 ISA_Input_flipflop.vhd<br>B.10 ISA_slave.vhd                                                                                                                                                                                                                                                                                                                                                         | <b>79</b><br><b>79</b><br><b>80</b><br><b>81</b><br><b>81</b><br><b>83</b><br><b>86</b><br><b>86</b><br><b>87</b><br><b>87</b>                                        |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd<br>B.7 IRQ_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.9 ISA_Input_flipflop.vhd<br>B.10 ISA_slave.vhd<br>B.11 LED_display4digit.vhd                                                                                                                                                                                                                                                                                                                           | 79<br>79<br>80<br>81<br>81<br>83<br>86<br>86<br>87<br>87<br>90                                                                                                        |

| APPENDIX B - SOURCE CODE.<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd<br>B.7 IRQ_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.9 ISA_Input_flipflop.vhd<br>B.10 ISA_slave.vhd<br>B.11 LED_display4digit.vhd<br>B.12 LVDS_master_transm_timer.vhd                                                                                                                                                                                                                                                                                     | 79<br>79<br>80<br>81<br>81<br>83<br>86<br>86<br>87<br>87<br>90<br>91                                                                                                  |

| APPENDIX B – SOURCE CODE.<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd<br>B.7 IRQ_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.9 ISA_Input_flipflop.vhd<br>B.10 ISA_slave.vhd<br>B.11 LED_display4digit.vhd<br>B.12 LVDS_master_transm_timer.vhd<br>B.13 Error_code_checker.vhd                                                                                                                                                                                                                                                      | 79<br>79<br>80<br>81<br>83<br>83<br>86<br>86<br>87<br>87<br>91<br>91                                                                                                  |

| APPENDIX B - SOURCE CODE.<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd<br>B.7 IRQ_timer.vhd<br>B.7 IRQ_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.9 ISA_Input_flipflop.vhd<br>B.10 ISA_slave.vhd<br>B.11 LED_display4digit.vhd<br>B.12 LVDS_master_transm_timer.vhd<br>B.13 Error_code_checker.vhd.<br>B.14 Data_reorder_lvds_in.vhd                                                                                                                      | <b>79</b><br><b>79</b><br><b>80</b><br><b>81</b><br><b>81</b><br><b>83</b><br><b>86</b><br><b>86</b><br><b>87</b><br><b>87</b><br><b>91</b><br><b>91</b><br><b>91</b> |

| APPENDIX B – SOURCE CODE.<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd.<br>B.7 IRQ_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.9 ISA_Input_flipflop.vhd<br>B.10 ISA_slave.vhd.<br>B.11 LED_display4digit.vhd.<br>B.12 LVDS_master_transm_timer.vhd<br>B.14 Data_reorder_lvds_in.vhd<br>B.15 Shift_sipo.vhd                                                                                                                                                                                                                          | 79<br>79<br>80<br>81<br>81<br>83<br>86<br>86<br>87<br>90<br>91<br>91<br>92<br>93                                                                                      |

| APPENDIX B - SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd<br>B.7 IRQ_timer.vhd<br>B.7 IRQ_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.9 ISA_Input_flipflop.vhd<br>B.10 ISA_slave.vhd<br>B.11 LED_display4digit.vhd<br>B.12 LVDS_master_transm_timer.vhd<br>B.13 Error_code_checker.vhd<br>B.14 Data_reorder_lvds_in.vhd<br>B.16 Shift_sipo_fullout.vhd                                                                                                                       | 79<br>79<br>80<br>81<br>81<br>83<br>86<br>86<br>87<br>90<br>91<br>91<br>91<br>93<br>93                                                                                |

| APPENDIX B - SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd<br>B.7 IRQ_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.9 ISA_Input_flipflop.vhd<br>B.10 ISA_slave.vhd<br>B.11 LED_display4digit.vhd<br>B.12 LVDS_master_transm_timer.vhd<br>B.13 Error_code_checker.vhd<br>B.14 Data_reorder_lvds_in.vhd<br>B.15 Shift_sipo_tullout.vhd<br>B.16 Shift_sipo_fullout.vhd<br>B.17 Master_node_state_machine.vhd                                         | 79<br>79<br>80<br>81<br>83<br>83<br>86<br>86<br>87<br>91<br>91<br>91<br>91<br>92<br>93<br>93<br>94                                                                    |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd.<br>B.7 IRQ_timer.vhd<br>B.7 IRQ_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.9 ISA_Input_flipflop.vhd<br>B.10 ISA_slave.vhd<br>B.11 LED_display4digit.vhd<br>B.12 LVDS_master_transm_timer.vhd<br>B.13 Error_code_checker.vhd<br>B.14 Data_reorder_lvds_in.vhd<br>B.15 Shift_sipo.vhd<br>B.16 Shift_sipo_fullout.vhd<br>B.17 Master_node_state_machine.vhd<br>B.18 Baud_rate_clk.vhd | 79<br>79<br>80<br>81<br>81<br>83<br>86<br>86<br>87<br>90<br>91<br>91<br>91<br>92<br>93<br>93<br>94<br>96                                                              |

| APPENDIX B - SOURCE CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79<br>79<br>80<br>81<br>81<br>83<br>86<br>86<br>87<br>90<br>91<br>91<br>91<br>91<br>92<br>93<br>93<br>94<br>96<br>97                                                  |

| APPENDIX B – SOURCE CODE<br>B.1 Error_code_generatior.vhd<br>B.2 Data_reorder_LVDS_out.vhd<br>B.3 Shift_PISO_nbit.vhd<br>B.4 VHDL_counter.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.5 Internal_register_manager_MNode.vhd<br>B.6 IRQ_out.vhd.<br>B.7 IRQ_timer.vhd<br>B.7 IRQ_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.8 ISA_bus_15us_timer.vhd<br>B.9 ISA_Input_flipflop.vhd<br>B.10 ISA_slave.vhd<br>B.11 LED_display4digit.vhd<br>B.12 LVDS_master_transm_timer.vhd<br>B.13 Error_code_checker.vhd<br>B.14 Data_reorder_lvds_in.vhd<br>B.15 Shift_sipo.vhd<br>B.16 Shift_sipo_fullout.vhd<br>B.17 Master_node_state_machine.vhd<br>B.18 Baud_rate_clk.vhd | 79<br>79<br>80<br>81<br>81<br>83<br>86<br>86<br>87<br>90<br>91<br>91<br>91<br>91<br>93<br>93<br>94<br>97<br>97                                                        |

| B.22 Shift_piso_nbit.vhd                 |                                        |

|------------------------------------------|----------------------------------------|

| B.23 I2C_register_selector.vhd           |                                        |

| B.24 Shift_sipo.vhd                      |                                        |

| B.25 I2C_start_signal_detector.vhd       |                                        |

| B.26 Internal_register_manager_SNode.vhd |                                        |

| B.27 IRQ_in.vhd                          |                                        |

| B.28 ISA_master.vhd                      |                                        |

| B.29 ISA_master_input_flipflop.vhd       | 109                                    |

| B.30 ISA_master_termination.vhd          | 109                                    |

| B.31 Slave_node_state_machine.vhd        |                                        |

| B.32 Slave_transm_timer.vhd              |                                        |

|                                          |                                        |

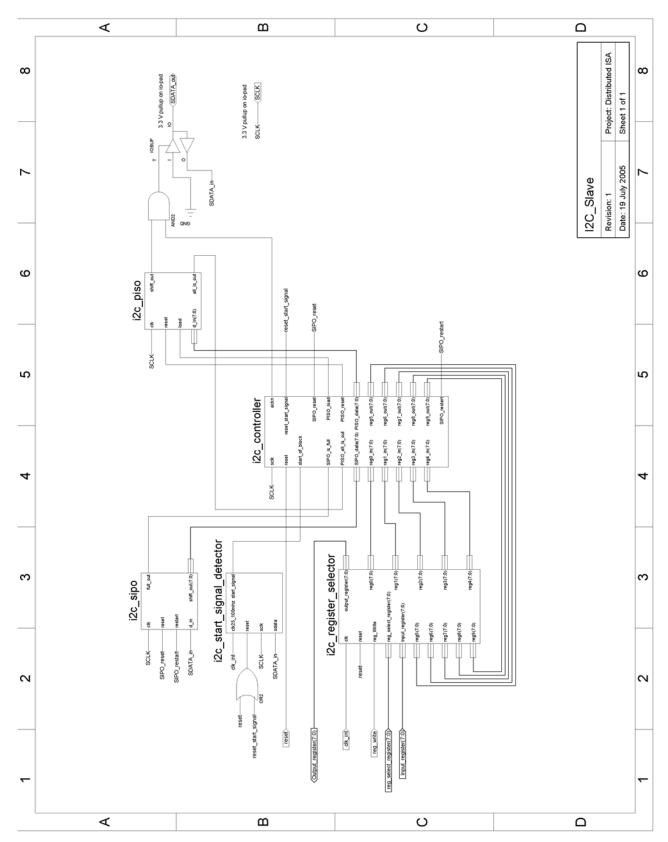

| APPENDIX C – SCHEMATIC                   | 113                                    |

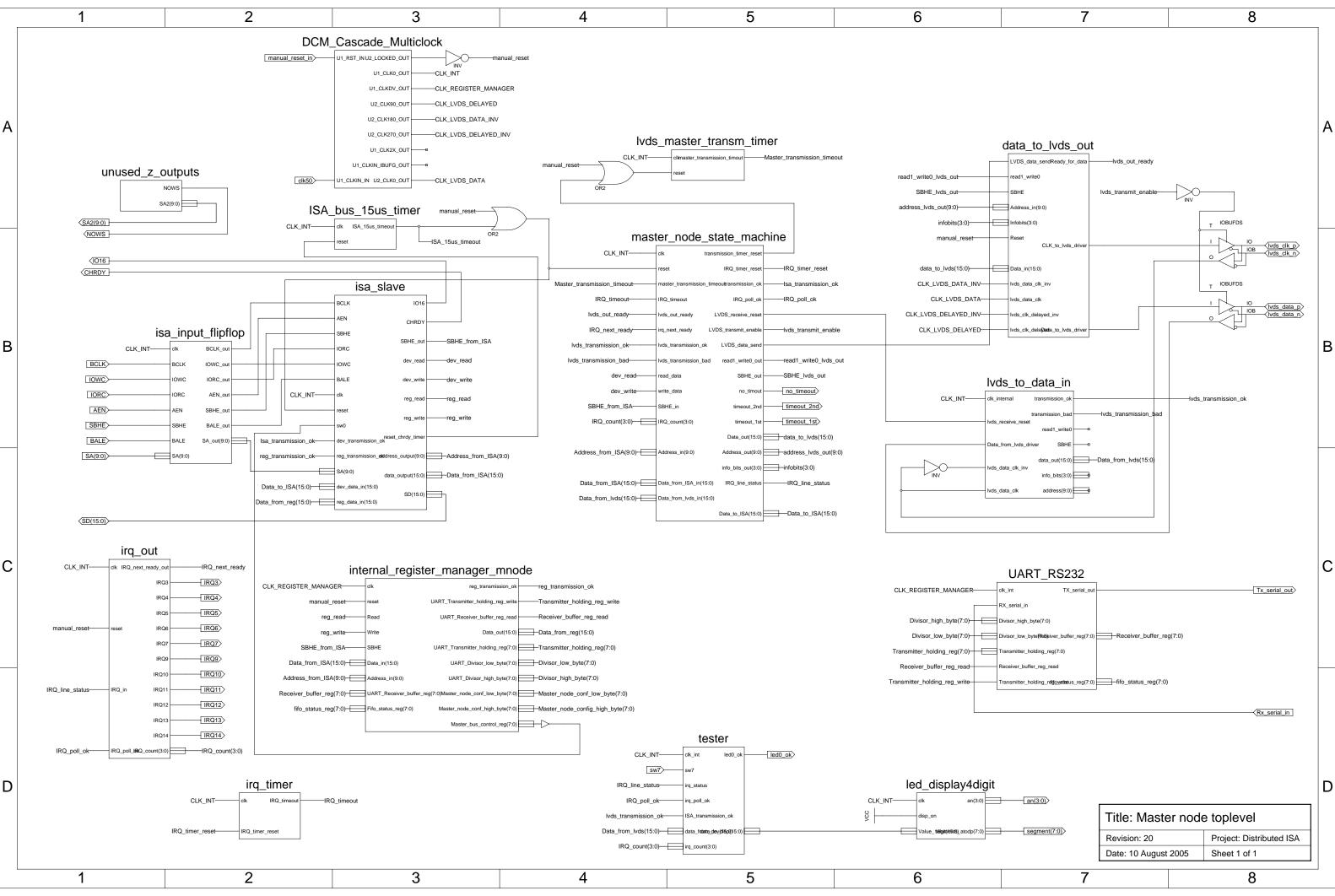

| C.1 Master_Node_top-level                |                                        |

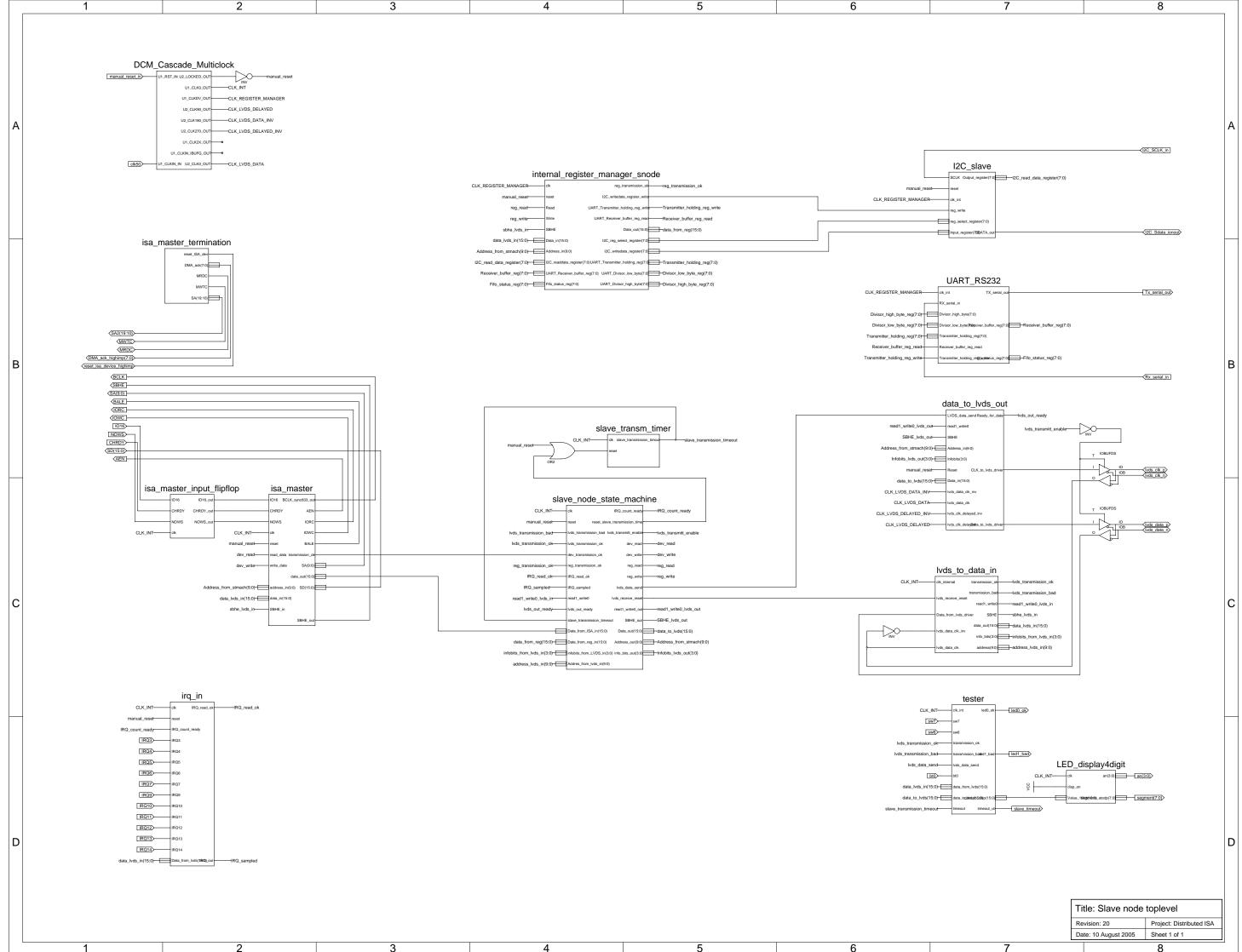

| C.2 Slave_Node_top-level                 |                                        |

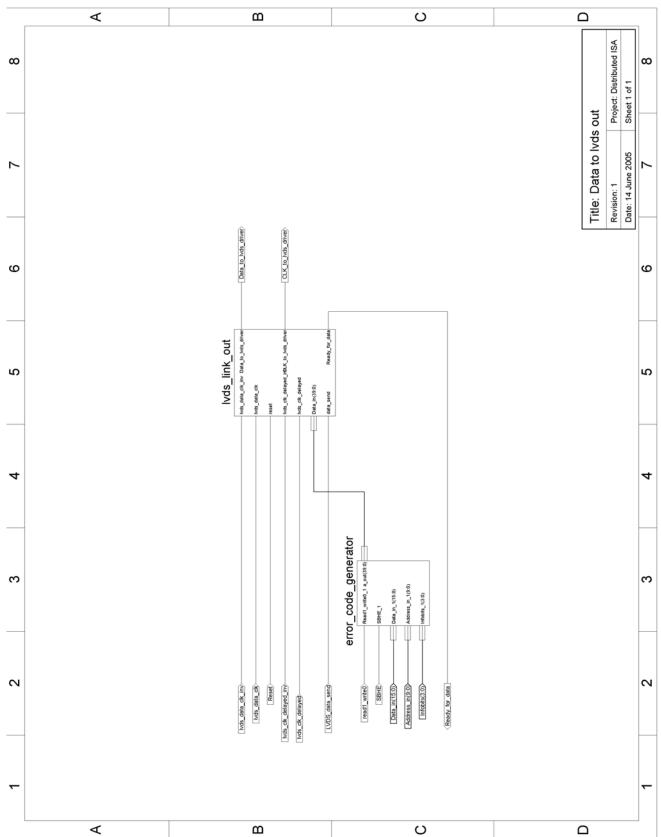

| C.3 Data_to_LVDS_out.sch                 |                                        |

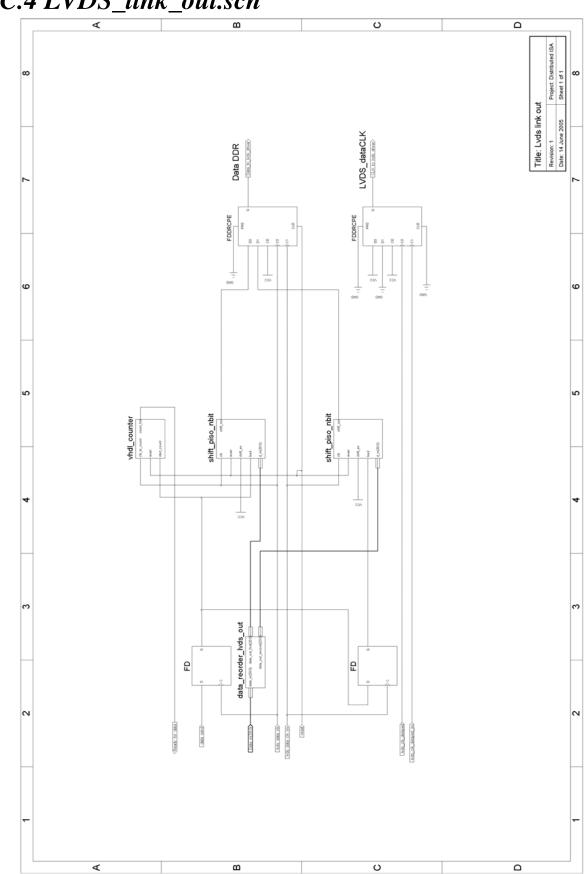

| C.4 LVDS_link_out.sch                    |                                        |

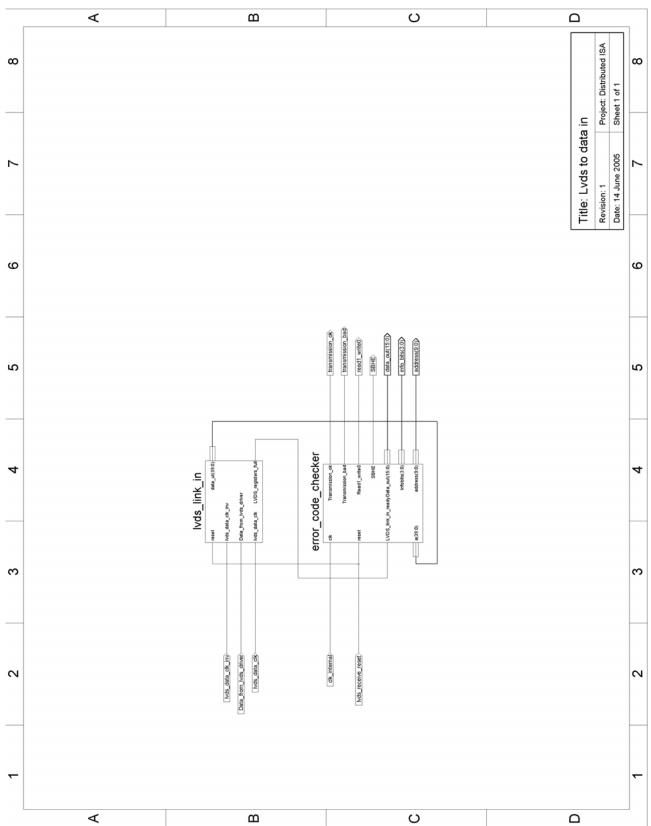

| C.5 LVDS to data in.sch                  |                                        |

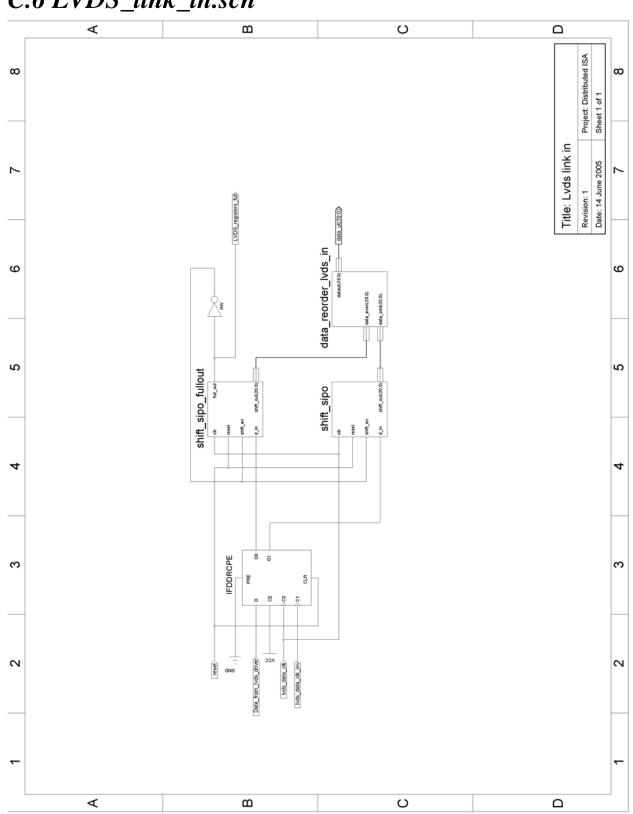

| C.6 LVDS_link_in.sch                     |                                        |

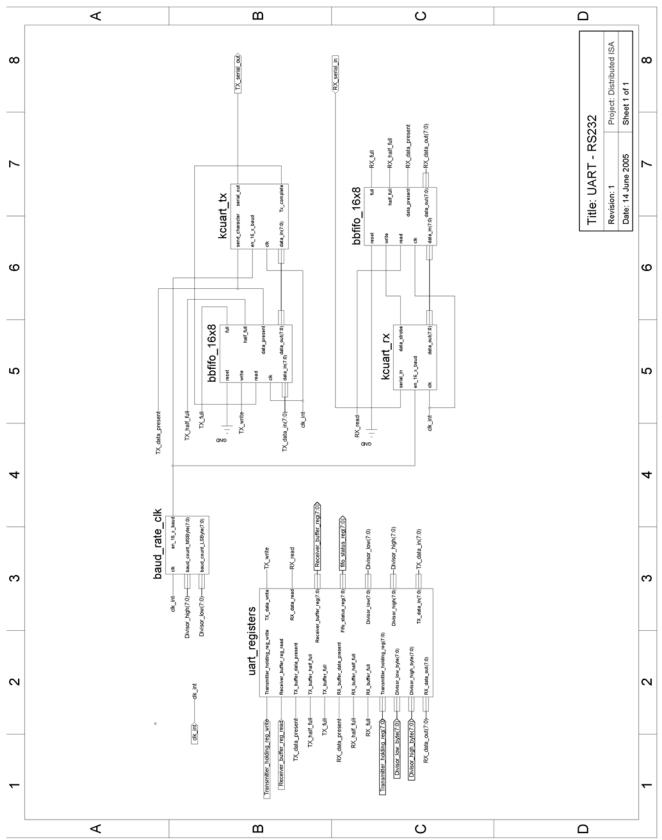

| C.7 UART_RS232.sch                       |                                        |

| C.8 I2C slave.sch                        |                                        |

|                                          |                                        |

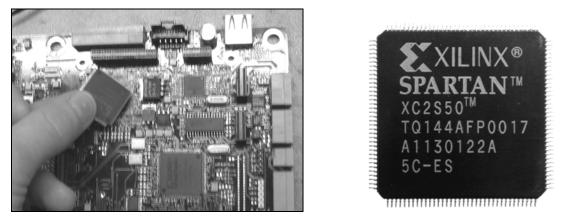

| APPENDIX D – PICTURES                    | 120                                    |

|                                          |                                        |

| ABBREVIATIONS                            | 122                                    |

|                                          | ······································ |

| ACKNOWLEDGEMENTS                         | 123                                    |

|                                          |                                        |

| INDEX                                    | 104                                    |

|                                          | 124                                    |

| REFERENCES                               | 400                                    |

|                                          | 126                                    |

## Figures

| Figure 1-1: PC/104 CPU Board - H6026 Pentium III with the size 90x96 mm.                                      | 8  |

|---------------------------------------------------------------------------------------------------------------|----|

| Figure 2-1: The seven-layer OSI reference model.                                                              |    |

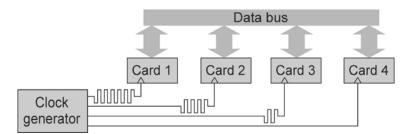

| Figure 2-2: Synchronous timing architecture using only one clock generator                                    | 13 |

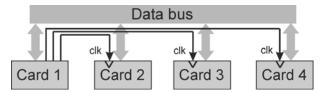

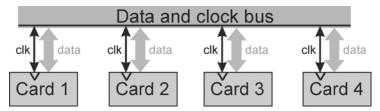

| Figure 2-3: Source synchronous clock design (showing clock signals from card 1 only)                          |    |

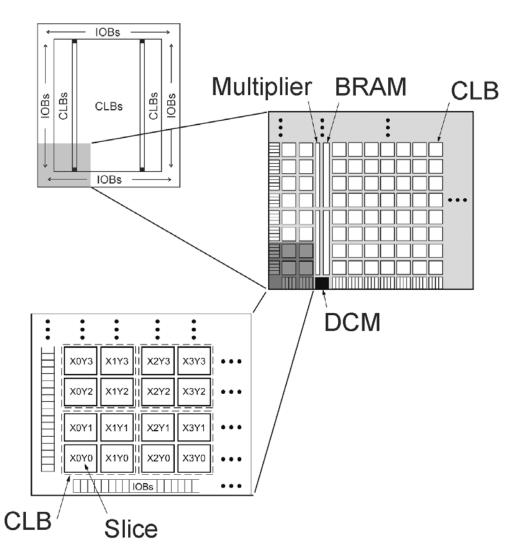

| Figure 2-4: The internal logical structure in the Spartan 3 FPGA                                              |    |

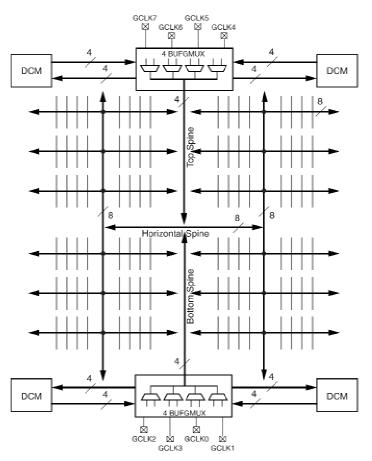

| Figure 2-5: The distributed clock network in the Spartan 3 FPGA                                               | 18 |

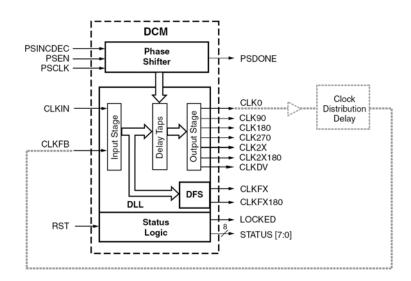

| Figure 2-6: The internal logical structure of the DCM in the Spartan 3 FPGA.                                  | 18 |

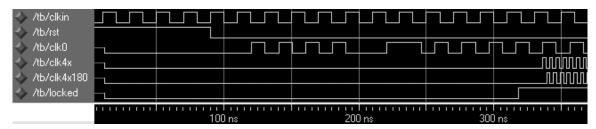

| Figure 2-7: The functional simulation of a DCM. 50 MHz input frequency and 200 MHz output                     |    |

| frequency                                                                                                     | 19 |

| Figure 2-8: The post-place and route simulation of a DCM. 50 MHz input frequency and 200                      |    |

| MHz output frequency                                                                                          | 20 |

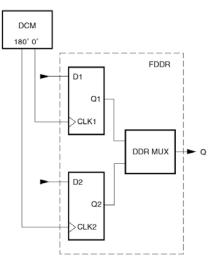

| Figure 2-9: The DDR component consisting of two flip-flops and one DDR MUX.                                   | 20 |

| Figure 2-10: This schematic shows two muxes serialising the data to the DDR component                         |    |

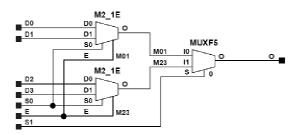

| Figure 2-11: Library Component M4_1E (4:1 MUX) implemented in a Spartan 3 FPGA                                | 21 |

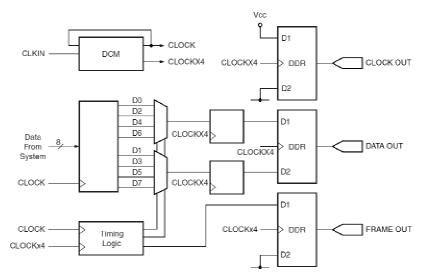

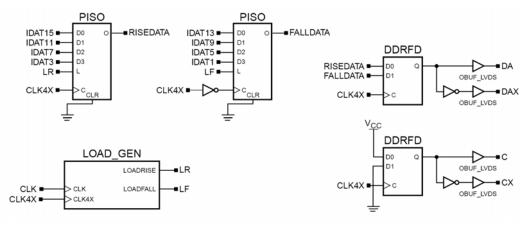

| Figure 2-12: This schematic shows two shift registers serialising the data to the DDR component               | 22 |

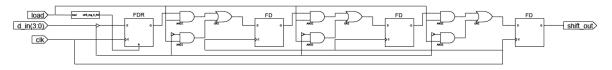

| Figure 2-13: A 4-bit shift register implemented in a Spartan 3 FPGA                                           | 22 |

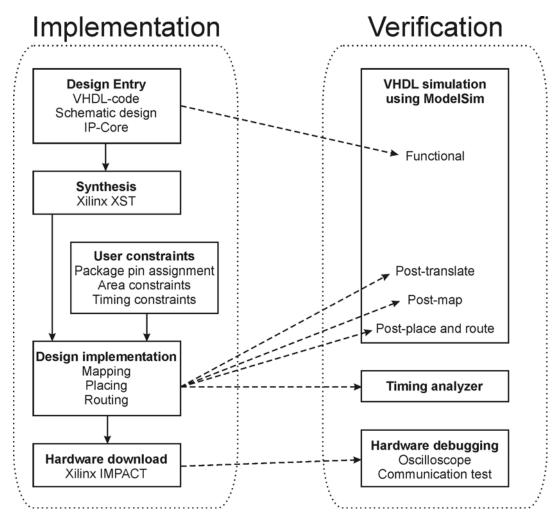

| Figure 2-14: The diagram shows the Xilinx ISE 7.1i design flow                                                | 23 |

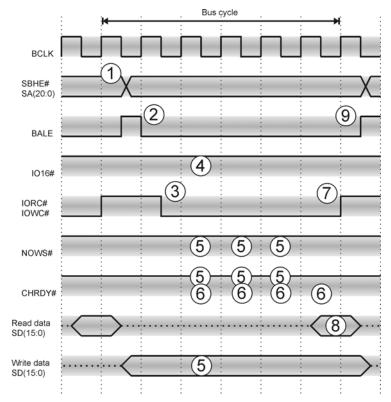

| Figure 2-15: ISA bus access to a standard 8-bit I/O device.                                                   | 26 |

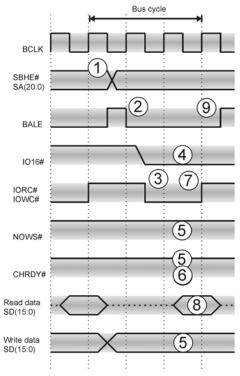

| Figure 2-16: ISA bus access to a standard 16-bit I/O device.                                                  | 26 |

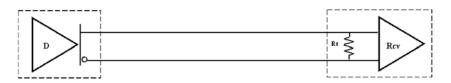

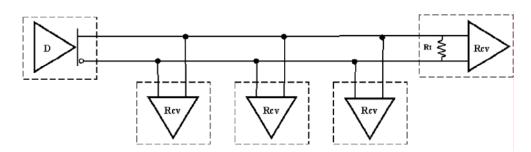

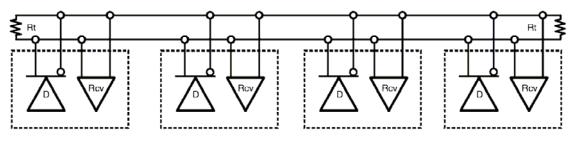

| Figure 2-17: LVDS point-to-point configuration.                                                               | 27 |

| Figure 2-18: LVDS multidrop configuration.                                                                    | 28 |

| Figure 2-19: LVDS multipoint configuration                                                                    | 28 |

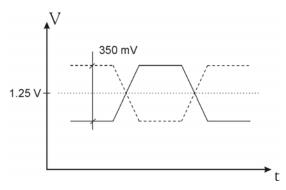

| Figure 2-20: The LVDS voltage levels typically used.                                                          | 28 |

| Figure 3-1: Modified source synchronous architecture. Both data and clock are sent in parallel                |    |

| on the bus                                                                                                    |    |

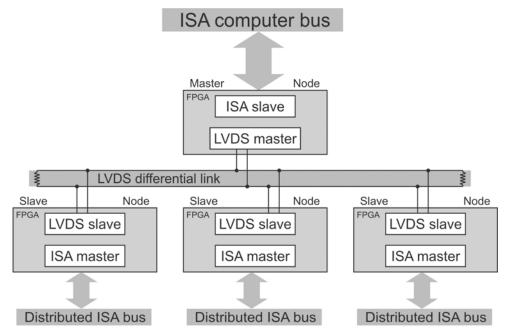

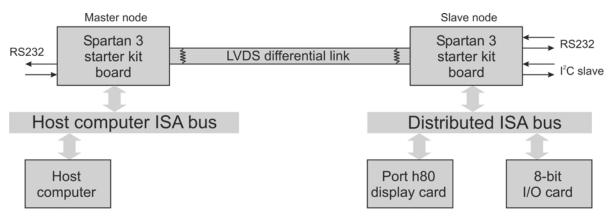

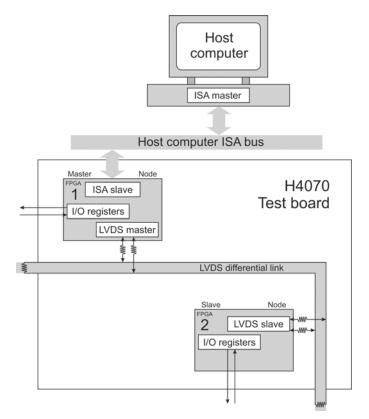

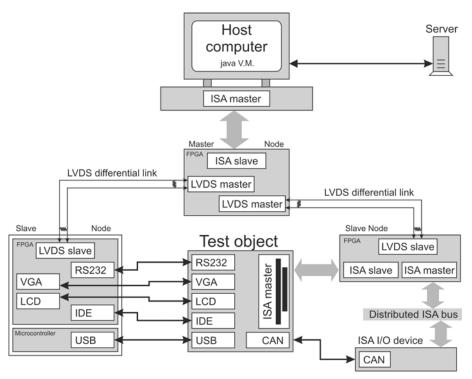

| Figure 3-2: Distributed ISA bus network connected using a LVDS link                                           |    |

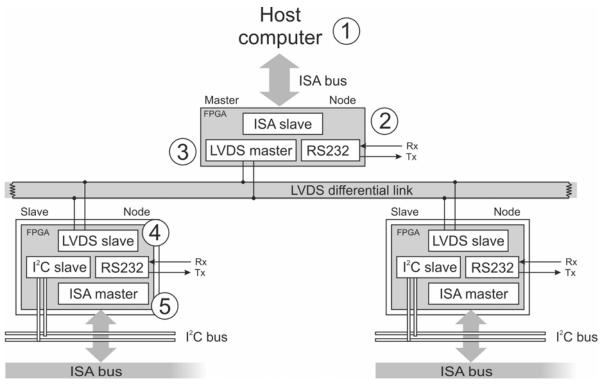

| Figure 3-3: The distributed ISA bus network design.                                                           |    |

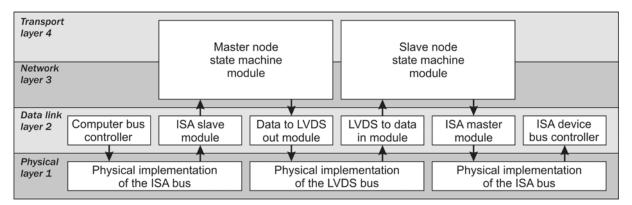

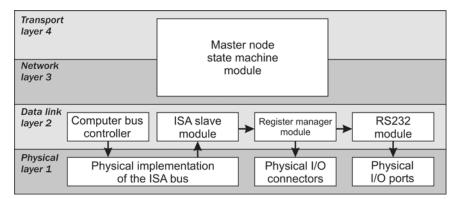

| Figure 3-4: The data flow during a distributed ISA bus access, presented using the OSI model                  | 35 |

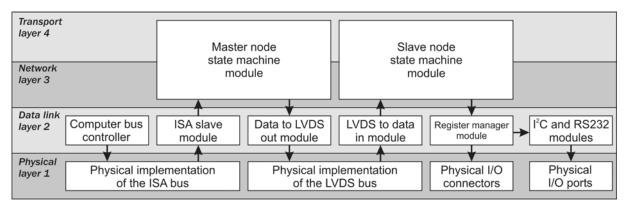

| Figure 3-5: The data flow during an access to an internal register, I <sup>2</sup> C or a RS232 module in the |    |

| master node. The flow is presented using the OSI model.                                                       | 35 |

| Figure 3-6: The data flow during an access to an internal register, I <sup>2</sup> C or a RS232 module in the |    |

| slave node. The flow is presented using the OSI model                                                         |    |

| Figure 3-7: The 40-bit LVDS data block (39:0)                                                                 | 36 |

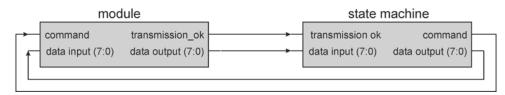

| Figure 3-8: Example of the internal asynchronous communication between components in the                      |    |

| FPGA                                                                                                          | 37 |

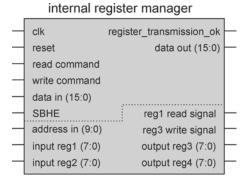

| Figure 3-9: The main input and output signals of the internal register manager module                         | 38 |

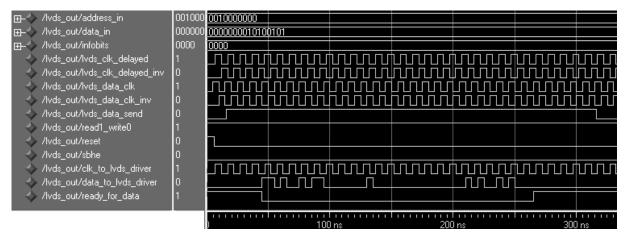

| Figure 3-10: Simulation of the LVDS data and clock signals generated from the LVDS out                        |    |

| module                                                                                                        |    |

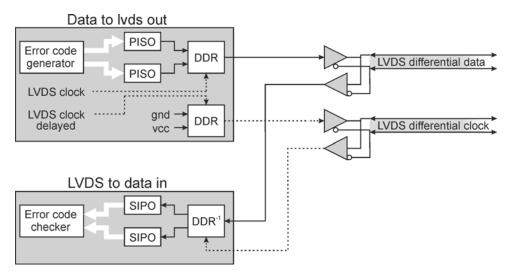

| Figure 3-11: The LVDS in and LVDS out modules                                                                 |    |

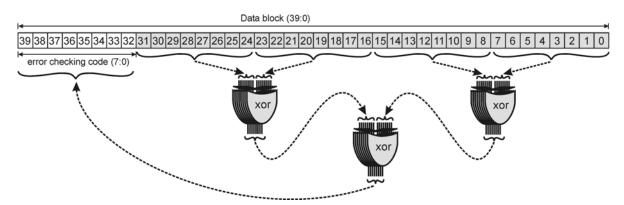

| Figure 3-12: Error code generation using XOR gates.                                                           | 42 |

| Figure 3-13: The arrangement of the two cascaded DCMs generating the clock signals driving                    |    |

| the FPGAs internal logic.                                                                                     |    |

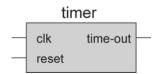

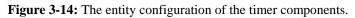

| Figure 3-14: The entity configuration of the timer components.                                                |    |

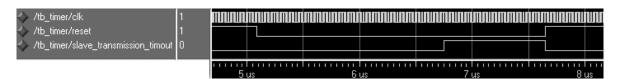

| Figure 3-15: Simulation of the LVDS slave transmission timer.                                                 |    |

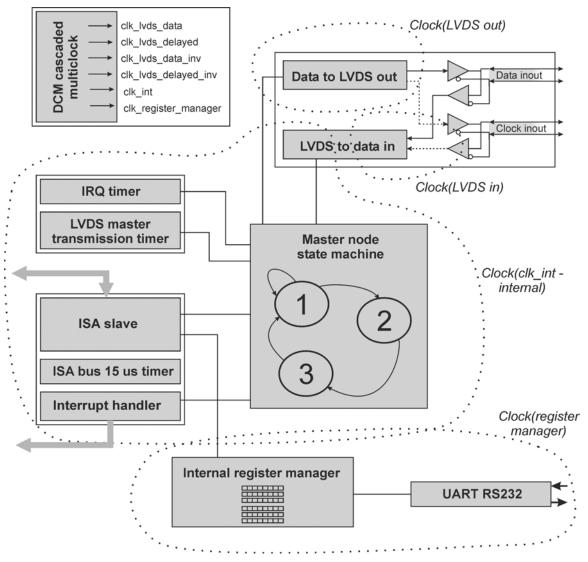

| Figure 3-16: Interconnection diagram of the main internal modules in the master node FPGA                     |    |

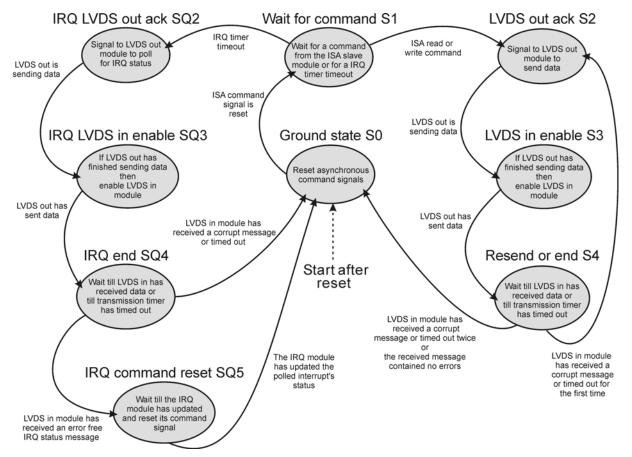

| Figure 3-17: State diagram of the master node state machine.                                                  |    |

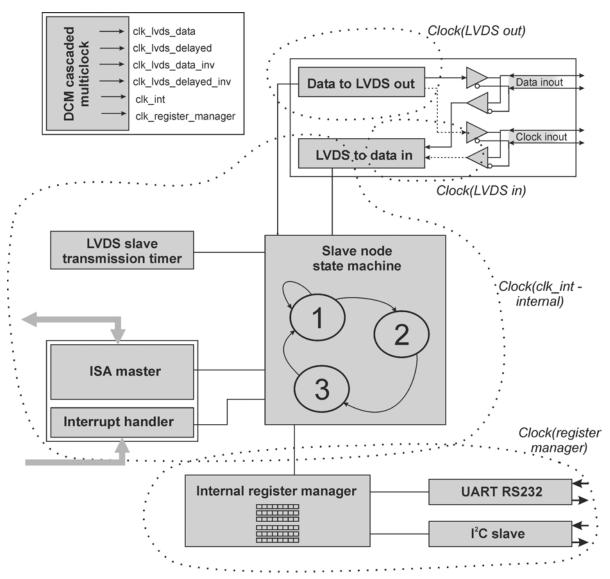

| Figure 3-18: Interconnection diagram of the main internal modules in the slave node FPGA                      |    |

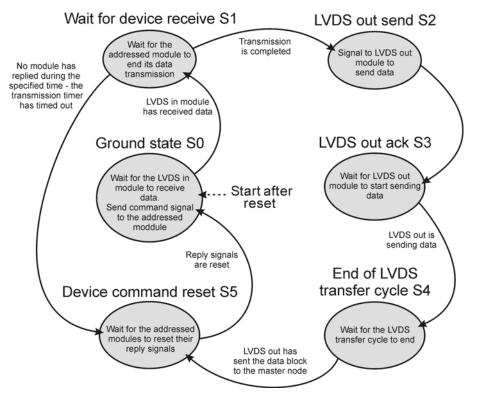

| Figure 3-19: State diagram of the slave node state machine.                                                   | 50 |

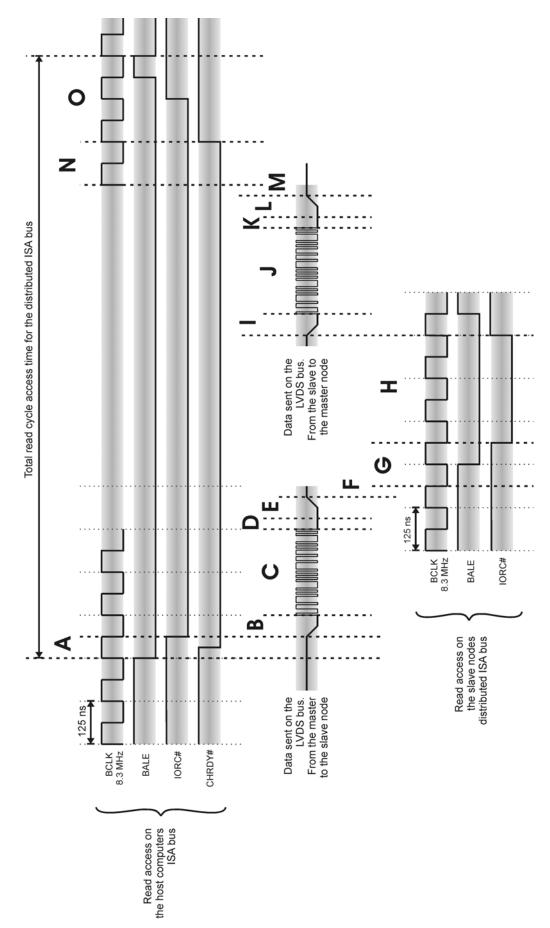

| Figure 3-20: The timing diagram shows a distributed ISA bus access made from the host                         | FO |

| computer                                                                                                      | 33 |

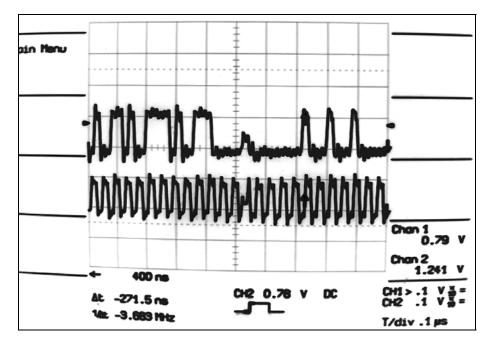

| Figure 4-1: Timing analysis of the LVDS link out component                                         | 57 |

|----------------------------------------------------------------------------------------------------|----|

| Figure 4-2: Timing analysis of the LVDS link in component                                          |    |

| Figure 4-3: Timing analysis of the slave node top-level design                                     | 58 |

| Figure 4-4: Timing analysis of the master node top-level design.                                   | 59 |

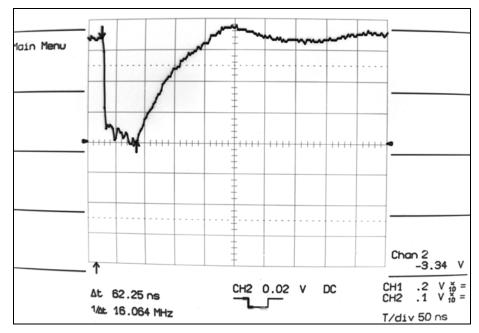

| Figure 4-5: An ISA bus access from the host computer to the master node in the distributed         |    |

| network. The upper channel displays the CHRDY signal and lower channel shows the                   |    |

| IOWC# generated by the host computer.                                                              | 61 |

| Figure 4-6: The channel shows an interrupt request generated by the distributed network            | 62 |

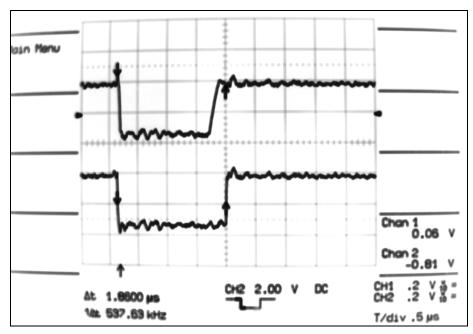

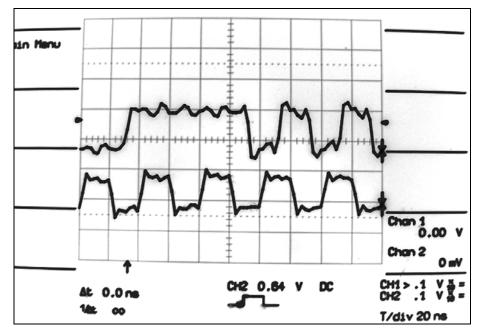

| Figure 4-7: LVDS signals using DDR. This means that one data bit is sampled at every rising        |    |

| and falling edge of the clock signal. The upper channel shows the data signal and the lower        |    |

| channel shows the clock signal.                                                                    | 62 |

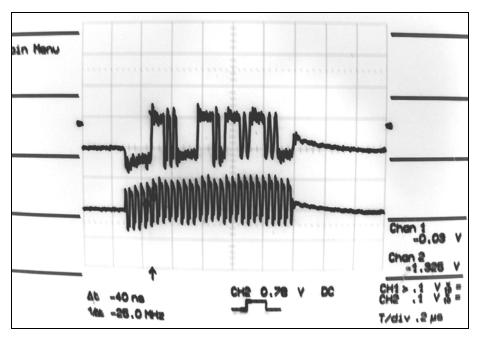

| Figure 4-8: Data request message sent from the master node to the slave node. The slave node       |    |

| did not send a reply message                                                                       | 63 |

| Figure 4-9: The last bits of a message sent using DDR and the bus is then released when no         |    |

| transmitter is driving it.                                                                         | 63 |

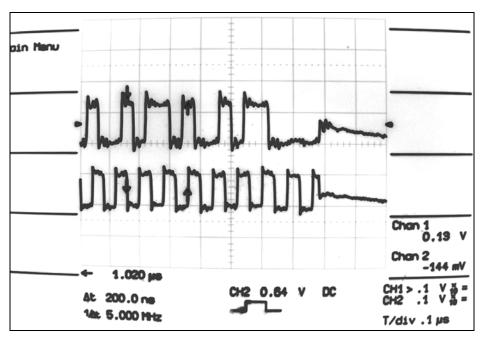

| Figure 4-10: The ending of a LVDS message requesting data from a register in a slave node          |    |

| FPGA and the beginning of the reply message generated by the slave node containing                 |    |

| the data in the accessed register. Notice the high impedence state in the middle when no           |    |

| driver is driving the bus                                                                          |    |

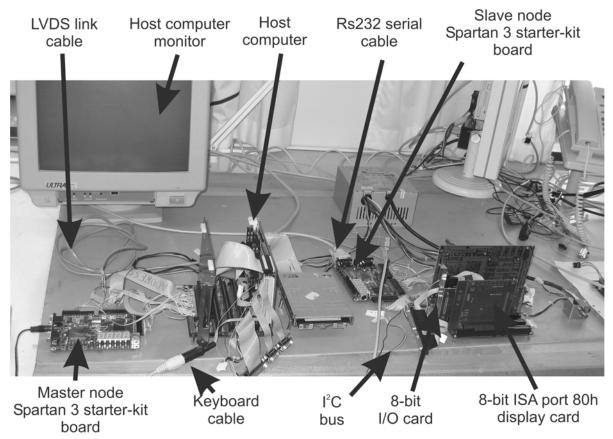

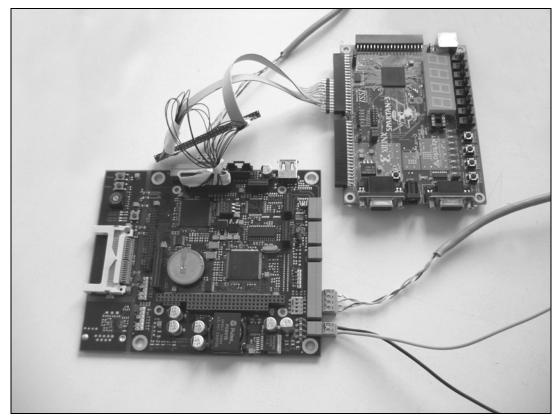

| Figure 4-11: The test set-up using two Spartan 3 starter kit boards                                | 64 |

| Figure 4-12: Test set-up using two Spartan 3 starter kit boards                                    | 65 |

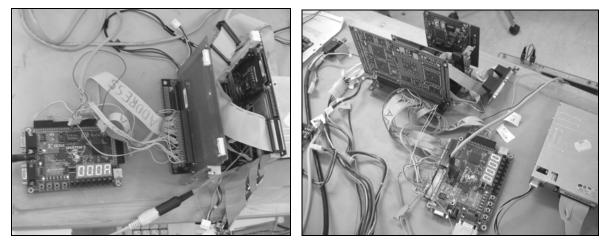

| Figure 4-13: Left: A Spartan 3 starter kit board programmed as a mater node connected to the       |    |

| host computer via the ISA bus. Right: A Spartan 3 starter kit board programmed as a                |    |

| slave node connected to one 8-bit I/O card and one port 80h display card                           | 65 |

| Figure 4-14: Set-up using one Hectronic H4070 board connected to the host computer via the         |    |

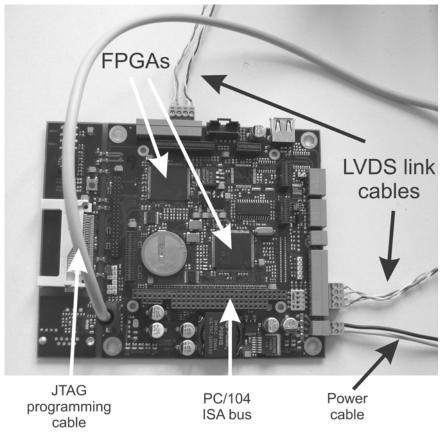

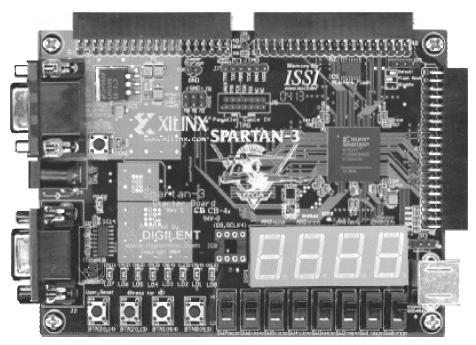

| ISA bus                                                                                            | 67 |

| Figure 4-15: The Hectronic H4070 test board                                                        | 67 |

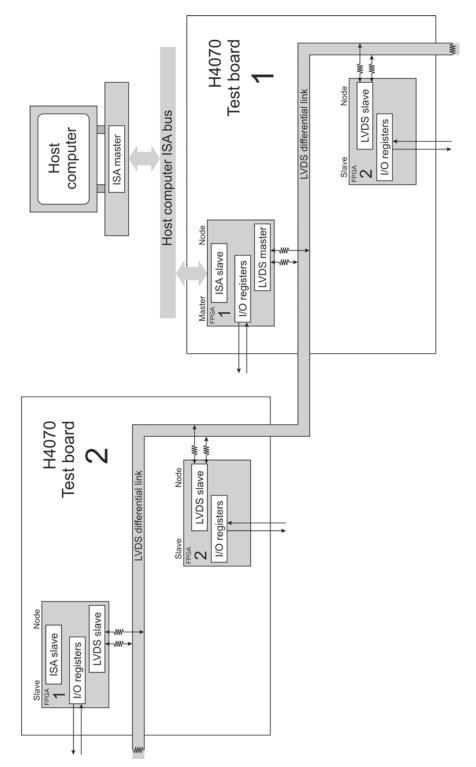

| Figure 4-16: Set-up using two Hectronic H4070 boards connected to the host computer via the        |    |

| ISA bus                                                                                            | 69 |

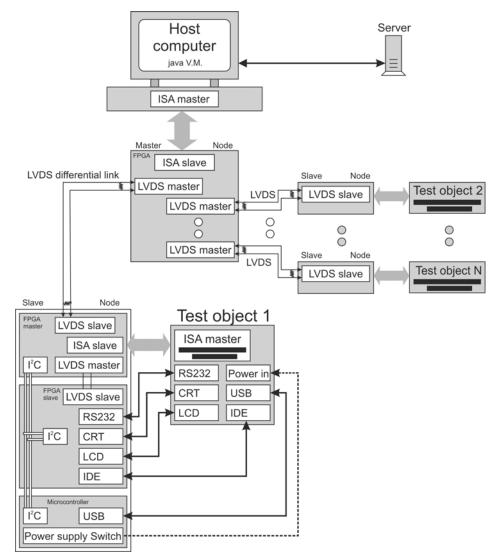

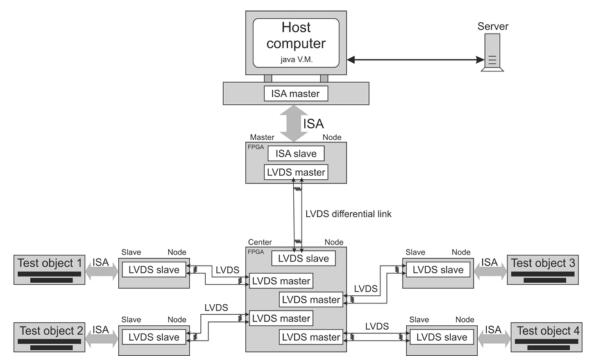

| Figure 6-1: A possible test configuration. All of the interfaces on the test objects are connected |    |

| to one slave node respectively                                                                     | 72 |

| Figure 6-2: A possible test configuration. The interfaces on the test object are connected to two  |    |

| slave nodes.                                                                                       | 74 |

| Figure 6-3: The distributed ISA bus network in a star configuration with an extra LVDS link        |    |

| from the master node to the center node                                                            | 74 |

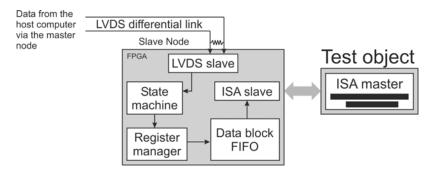

| Figure 6-4: Possible implementation of the program upload to the test object using a data block    |    |

| FIFO.                                                                                              | 75 |

## Tables

| Table 3-1: Register addresses in the distributed system                                       | 39 |

|-----------------------------------------------------------------------------------------------|----|

| Table 3-2: Bit functions of the master bus controller register.                               |    |

| Table 3-3: Bit functions of the FIFO status register.                                         | 40 |

| Table 3-4: Registers in the I2C module                                                        | 40 |

| Table 3-5: Master node timing constraints.                                                    | 48 |

| Table 3-6: Master node utilisation summary using the Spartan 3 xc3s200 FPGA device with       |    |

| the ft256 package.                                                                            | 48 |

| Table 3-7: Slave node timing constraints.                                                     | 51 |

| Table 3-8: Slave node utilisation summary using the Spartan 3 xc3s200 FPGA device with the    |    |

| ft256 package.                                                                                | 52 |

| Table 3-9: The access time to the distributed ISA bus compared to the ordinary ISA bus access | 54 |

|                                                                                               |    |

## Chapter 1 – Introduction

This master thesis describes the implementation of a data network that encapsulates and distributes the ISA bus protocol by the use of a LVDS<sup>I</sup> link. The hardware logic in this network consists of Spartan 3 FPGAs<sup>II</sup>.

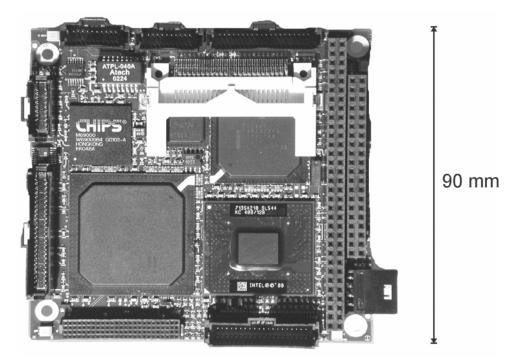

This work has been performed at Hectronic AB in Uppsala, Sweden. Hectronic AB is the leading Swedish embedded ICT technology supplier and develops small PC-cards. Several of these small PC-cards follow the PC/104 standard and may for example have integrated LCD graphics, serial ports, USB support, disk interface and 10/100Mbit Ethernet. These cards are widely used by the industry, where their small size is a big advantage for built-in applications. Figure 1-1 shows the PC/104 card H6026 Pentium III produced by Hectronic AB.

At different development stages these PC-cards have to be tested. The purpose of the test system is to test a PC-card as thoroughly as possible and generate a diagnostic report. The present test system has shortcomings and has to be improved in several ways. The motivation for this thesis is to improve the present test system.

Figure 1-1: PC/104 CPU Board - H6026 Pentium III with the size 90x96 mm.

### 1.1 The present test system

When the PC-card powers up the BIOS code first runs a series of diagnostic routines called POST<sup>III</sup>. It tests CPU, memory, keyboard, floppy and other basic functions. At the start of each routine the BIOS sends data to port 80<sup>IV</sup> that indicates what routine is being run. These codes are usually also sent via a serial port and if the POST-test stalls, the latest written code to port 80 will show which test went wrong.

<sup>&</sup>lt;sup>1</sup> Low Voltage Differential Signalling.

<sup>&</sup>lt;sup>II</sup> Field Progammable Gate Array.

<sup>&</sup>lt;sup>III</sup> Power On Self Test.

<sup>&</sup>lt;sup>IV</sup> Port 80 is a hexadecimal data address on the ISA bus.

After the POST-test, an operating system is loaded and started. The operating system will perform a series of peripheral tests of chosen ports and buses on the card. Several different tests may be performed when the operating system has been loaded. The result is reported back to the host computer<sup>I</sup> via the serial port.

#### 1.1.1 Problems with the present test system

One problem with the present test system is that it takes rather long time to load the operating system onto the board so that more advanced tests can be performed. Another delay is when the VGA bus is tested. Here, a LCD display is connected to the bus and the test personnel controls if the LCD display looks ok. If this control would be automatic, even more time could be saved. Also, more specified error reports are desired when an error is found. This is to be able to pinpoint the error source as fast as possible.

All the cases mentioned above contribute to the total test time for every board. If these problems could be solved or minimized, test time would be significantly reduced and the test costs would be lower.

### 1.2 Requirements for a new test system

A small group of employees were put together to discuss a new test system. The group determined some guideline properties needed in the test system. The directions are presented in this section.

#### 1.2.1 The properties of the test system

The test system should have the following properties:

- **Test of the test objects<sup>II</sup> peripherals:** The buses and ports of the test object should be able to be connected to the test system so that communication tests of these peripherals can be performed.

- Fast uploading of data to the test object: To save test time, the uploading of the operating system from the host computer to the test object has to be fast. 1 Mbyte/s and faster was estimated to be sufficient.

- **Flexibility:** The test system should be able to be reconfigured to support other peripheral tests to update possible programming errors in the existing code. The test system should also be able to be expanded to test several test objects all connected to the system at the same time.

- **Distance between two network nodes:** Because several test objects might have to be tested at the same time the network has to support distances up to about 2 meters.

- **Connection wiring:** To connect the network a small bus of a maximum width of five wires are required. This is to make the test system able to be modified into other small future applications.

- **Supply voltage:** The five available wires should carry supply voltage for the distributed system nodes as well. This is not necessary for the test system, but is required in some applications planned for the future.

- **Cost:** The logic chosen should be low cost.

<sup>&</sup>lt;sup>I</sup> The host computer is the main computer coordinating the test.

<sup>&</sup>lt;sup>II</sup> The test object is the fabricated circuit board that is to be tested.

#### 1.2.2 Different test situations

There are several test situations to be considered. These are summarised below:

- Lab test: During the design and development of a card, different tests of the card should be performed.

- **Function test:** This test is made after the final assembly of the cards. If the card passes this test, it should be fully functional.

- **Temp test:** Here the card is tested at different temperatures. The card functionality is tested while it is exposed to different temperatures in a special designed temperature box. To save testing time several cards need to be tested in the box at the same time. This demands the test system to support several cards to be connected simultaneously.

- **Field test:** If an error occurs after delivery, it is a big advantage if the card could be tested "in the field" by the customer.

#### 1.2.3 Test system architecture

The test system should consist of one host computer running the main test program coordinating the tests. The host computer should be able to upload program code to the test object(s) via the test system. The host computer should also be able to communicate via the test system to the peripherals of the test object.

After performing the test, it would be an advantage if the host computer could report the result to a data server logging all the tests.

## 1.3 The aim of this project

The aim of this project is mainly to develop a distributed system suitable to handle the communication between the host computer and the test object(s) and its peripherals. The problems with the present system and the requirements of a new system should be considered in the new design.

## 1.4 Method description

The implementation of the logic is to be done on a suitable CPLD<sup>I</sup>/FPGA. The proper CPLD/FPGA has to be chosen and suitable programming technologies in the device have to be investigated. The programming language used to design the logic is VHDL.

Because a new distributed network has to be designed, suitable system topologies and channel configurations has to be investigated as well.

<sup>&</sup>lt;sup>I</sup> Complex Programmable Logic Device.

## Chapter 2 – Background

This chapter introduces the technologies used in the distributed network design. It also forms a basis for the decisions made in section 3.1. This chapter could be used as a reference when different implementations, using these technologies, are described in other chapters.

## 2.1 The OSI seven-layer model

OSI<sup>I</sup> is a standard reference model of the communication flow between two end users in a network. The International Organization for Standardization developed OSI in 1984 and it describes a framework for implementing network protocols in seven layers. The OSI seven-layer model is a part of this standard and is a useful reference model for describing and designing computer networks.

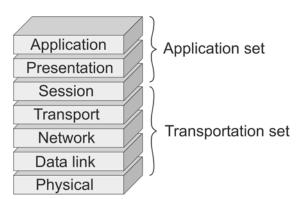

The OSI seven-layer model consists of seven layers that data has to go through to travel from one user to another. Control is passed from one layer to the next and each layer uses the functions of the layer below and only exports functionality to the layer above. The data-flow starts from the application layer in one station and proceeds to the bottom layer. There it passes over a channel and travels back up in the layer hierarchy in another station. The seven layers are shown in Figure 2-1 and are briefly described below [1]:

- Layer 7 Application: This layer interacts with the application and supplies network related activities such as file transfers.

- **Layer 6 Presentation:** This layer is usually part of an operation system and converts incoming and outgoing data from one presentation format to another. For example it could convert a data steam into a popup window displaying some information.

- Layer 5 Session: Establishes, maintains and ends communication with the accessed device.

- Layer 4 Transport: Ensures a complete data transfer. For example by performing error checking and controlling that all the packages has arrived.

- Layer 3 Network: Network data routing and flow control. The way the data is to be sent is determined in this layer.

- Layer 2 Data link: Describes the logical organisation of data bits transmitted, such as framing, addressing and error checking. Error checking may occur in a higher layer as well.

- Layer 1 Physical: Describes the physical hardware properties of the channel such as connectors, voltage levels and timing.

Figure 2-1: The seven-layer OSI reference model.

<sup>&</sup>lt;sup>I</sup> Open System Interconnection.

## 2.2 Backplane architecture

A backplane is used to join several peripherals together. The VME, PCI and ISA buses are examples of protocols using backplanes. A backplane set-up could for example be a microprocessor communicating with memory, keyboard, mouse and soundcard devices. The need for backplane performance has always been high. The maximum number of cards connected to one segment<sup>1</sup>, data path width, hot-swap<sup>II</sup> capabilities and low cost are concerns to have in mind when designing a high performing backplane. In this section, some important design methodologies are explained [2].

#### 2.2.1 Connectivity

Backplane connectivity refers to how the drivers and receivers are connected. There are two commonly used transmission schemes today, serial and parallel.

#### 2.2.1.1 Parallel design

In this design, the bits are sent from the driver in parallel. All the information sent in the backplane is configured either as multipoint or multidrop [2].

The advantages of a parallel design are summarised below:

- Individual lines can be used as control signals with fast reaction times.

- High data throughput can be achieved with low signal speed.

- No extra logic is needed to serialise and deserialise the data blocks. This means no time delay.

The disadvantages of a parallel design are:

- Many data traces are needed. This means lots of space on the circuit board and high costs.

- The signal skew between the signal lines has to be matched.

- Impractical when going between units at long distances.

#### 2.2.1.2 Serial design